-

01-1.패터닝 기술

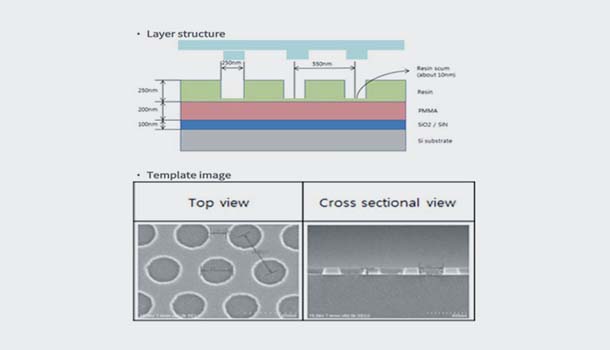

나노 임프린트 기반 나노홀 어레이 템플릿 제조 기술 : 대면적의 Nano scale structure 구현을 위해서는 E-beam lithography 방식으로는 비용적인 측면에서 한계가 존재함. 그 대안으로 Nanoimprint lithography 방식을 통한 Wafer level의 SiO2 nano hole template을 구현한 결과.

-

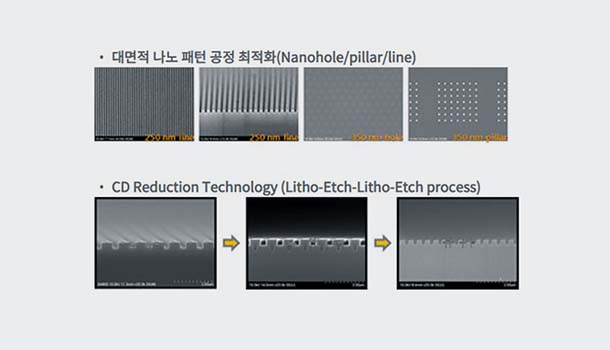

01-2.패터닝 기술

액체 혹은 기체 상태의 물질을 각각의 목적에 맞는 분리와 합성 등을 거쳐 유기화합물의 구조, 성분을 정량시키는 것으로 NMR, GC/MS, LC Q-TOF 를 활용하여 도출 할 수 있다.

-

02.식각 기술

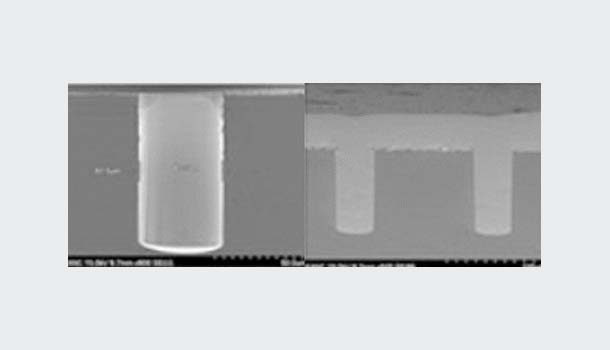

- Lithography의 한계성과 소형화에 따른 고집적, 고밀도의 반도체 제조를 위해 TSV (Through Silicon Via) 3D 적층 패키지 기술이 필요.

- 기존 와이어 본딩 패키지나 플립칩 패키지에 비해 전력손실 적고, 동작속도 빠름

- Si Etch를 통한 Hole 및 Via 형성과 Hole 및 Via에 Seed Metal 증착의 Step Coverage 그리고 Cu전기도금을 이용한 Hole 및 Via의 Cu 충진이 중요 이슈

- 기술적 가치

- 고집적 가능한 반도체 소자로 성능 향상

- 모바일기기의 배터리 소모 감소

- 전력손실 최소화

-

03.박막 기술

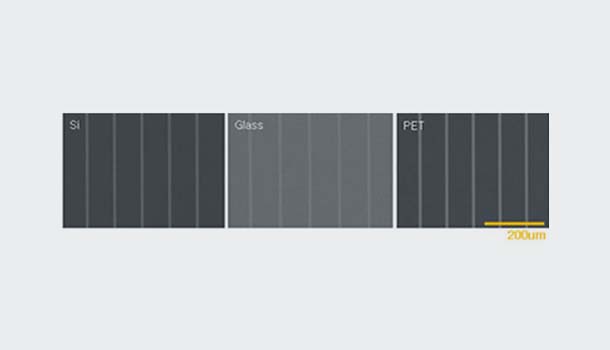

- 기존 evaporation 장비 사용 시 증착 후 추가 열처리 공정 필요 (550도~600도 수준)

- glass, flexible 기판에서는 열처리 공정 불가(기판 손상 등의 문제점 존재)

- Wsputtering을 통한 ITO Lift off 공정 개발 필요

- Si / Glass / Flexible 기판 등 다양한 기판에서 ITO 패턴 구현 가능

- 기술적 가치

- 다양한 반도체 소자의 전극으로서 사용 가능

- 추가 열처리 공정 불필요